一文搞懂CPU的工作原理(下):详解CPU的功能与运作方式

【干货】一文搞懂CPU的工作原理

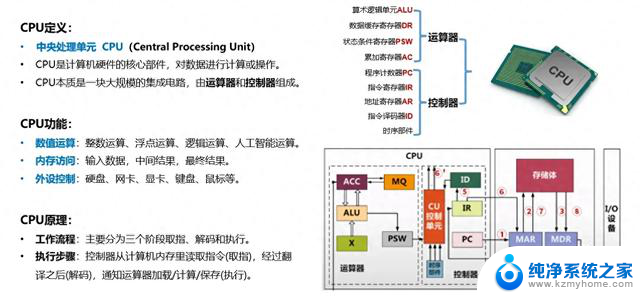

中央处理器(Central Processing Unit,简称CPU)是一块由超大规模集成电路组成的运算和控制核心。主要功能是运行指令和处理数据。

CPU是计算机系统中的核心组件,从诞生到现在,主要在两个维度上做了很大的提升,一个是制造工艺,另一个是设计思想,需要回顾下计算机体系结构。

在第一台计算机诞生时,很多逻辑都是硬化在电路板上,软硬件耦合严重,这就导致一旦修改程序,就要重新组装电路板的问题,使得编程效率很低。当时,冯·诺依曼提出了一个至关重要的设计思路:计算机要有一定的逻辑结构,将软硬件分离,要求CPU顺序地从存储器中取出指令和数据,然后进行相应的计算。

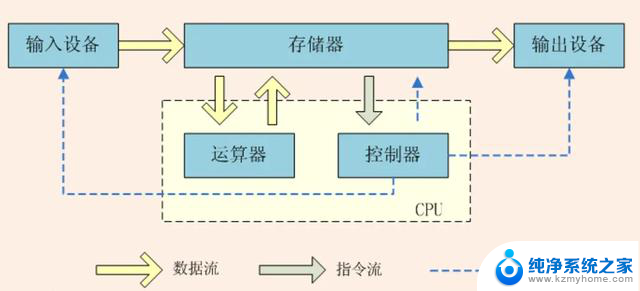

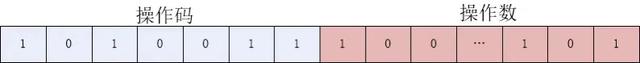

其确定了计算机的五个基本组成部分:运算器、控制器、存储器、输入设备、输出设备。其中指令、数据都是存在主(内)存储器中,以便于CPU在工作时,能够高速地从存储器中提取指令,并加以分析和执行。程序、数据的最终形态都是二进制编码,存储在存储器中,二进制编码也是CPU能够识别、执行的编码。

图片

冯·诺依曼体系结构

其实,冯·诺依曼体系结构存在一些问题,但是人们在它之上做了改进:

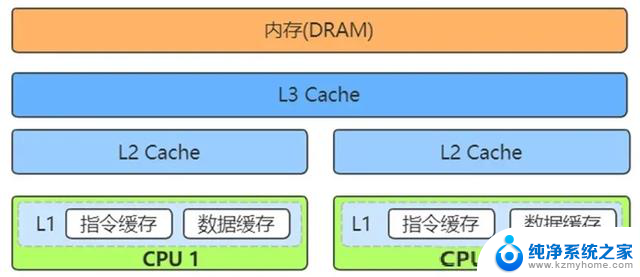

1)指令和数据公用内存,即指令和数据都存在一个存储器上,并通过一个系统总线进行访问。由于主存的读写速度跟不上CPU运行速度,所以在CPU和主存间增加了高速缓存,并在L1高速缓存中区分了指令缓存和数据缓存,进一步提升系统总线访问速度。(扩充:为了解决指令和数据共用系统总线带来速度慢的问题,又提出了哈佛架构。即将指令和数据分别存放在不同的主存上,可以并行访问,但由于哈佛架构复杂,不适合外部主存的扩展,所以并未得到广泛应用。)

2)指令顺序指令:指令只能顺序,在一个pipe上运行。为了提升指令运行速度增加了,乱序执行、多级流水线、分支预测等功能。

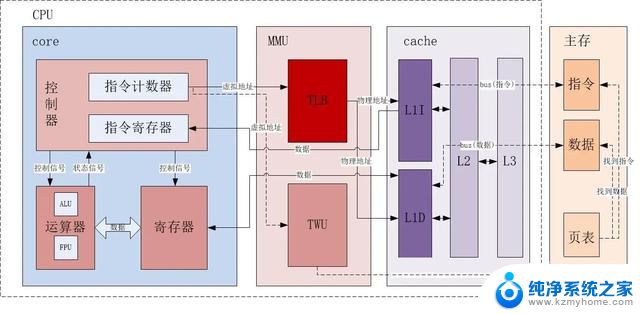

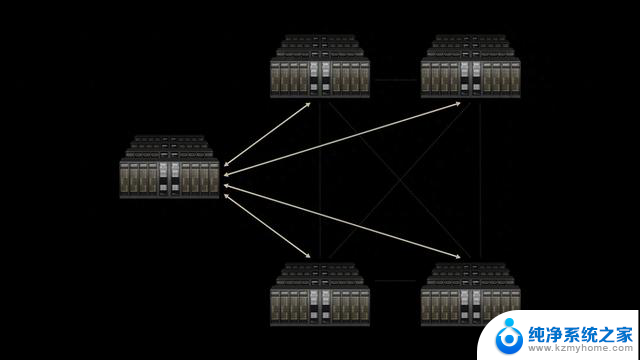

目前,现在计算机的主流框架方案是采用CPU+外部存储,其中CPU内部包含CPU核心(Core)、内存映射单元(MMU)、缓存(Cache)等组成。

图片

CPU+外部存储的框架

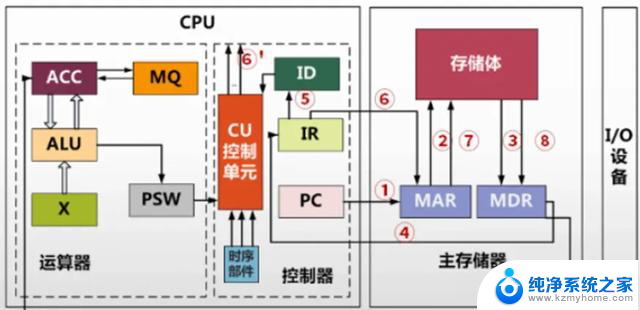

1)CPU核心(Core):根据指令进行各种处理的电子电路。一般由控制器、运算器、寄存器组成。

控制器,(Control Unit,简称CU),是计算机的指挥中心,只有在它的控制下,整个CPU才能够有条不紊地工作、自动执行程序。CU包括指令寄存器、指令计数器,其中指令寄存器存放当前正在执行的指令,指令计数器总是指向下一条要执行指令的地址。

运算器,是一个负责算术运算和逻辑运算的模块。主要包含算术逻辑单元(Arithmetic Logic Unit,简称ALU)和浮点运算单元(Floating Point Unit,简称FPU)。ALU的主要功能:在控制信号的作用下,完成加、减、乘、除等算术运算,以及与、或、非、异或等逻辑运算以及移位、补位等运算。FPU主要负责浮点运算和高精度整数运算。有些FPU还具有向量运算的功能。

寄存器,主要功能是存储数据、地址及指令,并且能够高速、自动地完成数据的存储。寄存器是有记忆功能的器件,而且采用两种稳定状态0或1来记录数据信息,所以CPU中的程序和数据,都要转换为二进制才可以存储和操作。寄存器也是由与、或、非逻辑门电路组成的。

2)内存映射单元(Memory Map Unit,简称MMU),指的是将虚拟地址转化成物理地址的模块。MMU包含了两个模块:页表查找表(Table Lookup Buffer,简称TLB)和页表遍历单元(Table Walk Unit,简称TWU)。

TLB是一个高速缓存,用于缓存页表转换的结果,从而减少页表查询的时间。一个完整的页表翻译和查找的过程叫做页表查询,页表查询是通过硬件模块TWU自动完成的,但是页表的维护需要软件来完成,且存放在主存中,因此页表查询是一个耗时的过程。当TLB未命中时,MMU才会通过TWU查询页表,从而得到翻译后的物理地址,这个虚拟地址及物理地址的映射也会存储在TLB中。

当TLB中缓存要访问的虚拟地址到物理地址的转换关系的时候,就可以直接找到的物理地址,通过该物理地址在L1 cache中查找数据。如果TLB中没有缓存要访问虚拟地址对应的物理地址,这时会通过页表遍历单元(TWU模块)遍历主存中的页表,查找相应的物理地址,找到后再通过这个物理地址访问L1 cache。

3)缓存(Cache):主要作用是CPU与主存的缓冲层,那么Cache的速度应该接近于CPU